3-Axis Gyro L3GD20 Carrier with Voltage Regulator

3-Axis Gyro L3GD20 Carrier with Voltage Regulator

Out of stock

Couldn't load pickup availability

Overview

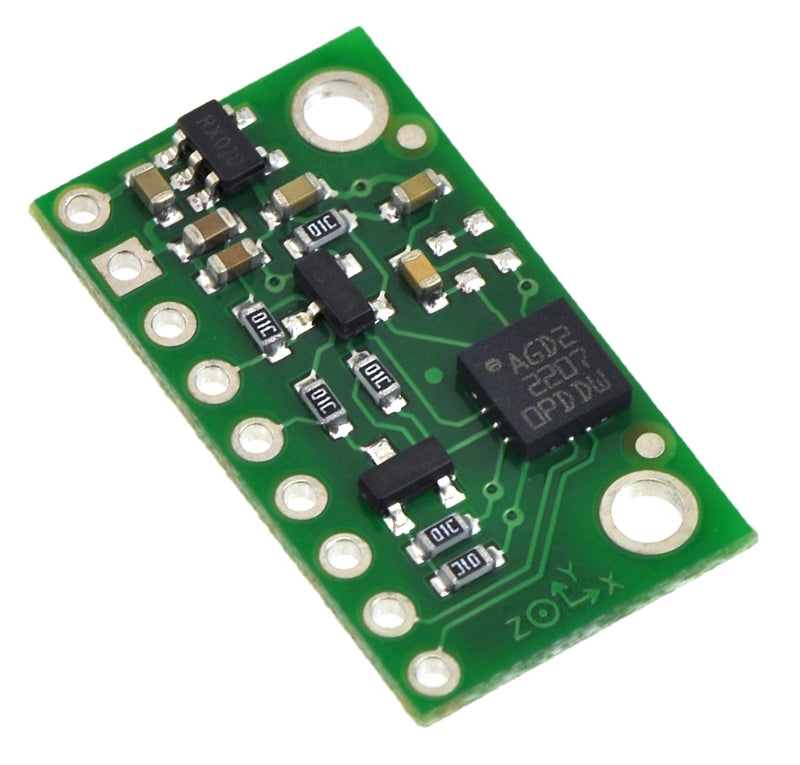

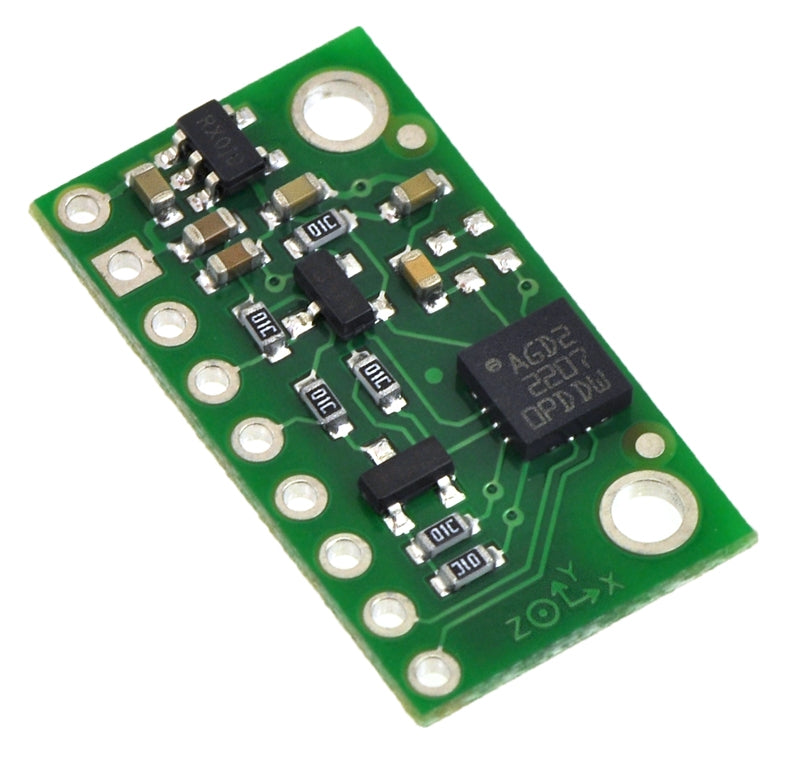

This board is a compact (0.5″ × 0.9″) breakout board for ST’s L3GD20 three-axis digital-output gyroscope; we therefore recommend careful reading of the L3GD20 datasheet(2MB pdf) before using this product. The L3GD20 is a great IC, but its small, leadless, LGA package makes it difficult for the typical student or hobbyist to use. It also operates at voltages below 3.6 V, which can make interfacing difficult for microcontrollers operating at 5 V. This carrier board addresses these issues by incorporating additional electronics, including a 3.3 V voltage regulator and level-shifting circuits, while keeping the overall size as compact as possible. The board ships fully populated with its SMD components, including the L3GD20, as shown in the product picture.

The L3GD20 has many configurable options, including three selectable angular rate sensitivities, a choice of output data rates, an embedded FIFO for buffering output data, and a programmable external interrupt signal. The three angular velocity readings are available through a digital interface, which can be configured to operate in either I²C or SPI mode.

The carrier board includes a low-dropout linear voltage regulator that provides the 3.3 V required by the L3GD20, which allows the sensor to be powered from a 2.5-5.5 V supply. The regulator output is available on the VDD pin and can supply almost 150 mA to external devices. The breakout board also includes a circuit that shifts the I²C/SPI clock and data in lines to the same logic voltage level as the supplied VIN, making it simple to interface the board with 5 V systems, and the board’s 0.1″ pin spacing makes it easy to use with standard solderless breadboards and 0.1″ perfboards.

Specifications

Dimensions: 0.5″ × 0.9″ × 0.1″ (13 × 23 × 3 mm)

Weight without header pins: 0.7 g (0.03 oz)

Operating voltage: 2.5 to 5.5 V

Supply current: 7 mA

Output format (I²C/SPI): one 16-bit reading per axis

Sensitivity range (configurable): ±250°/s, ±500°/s, or ±2000°/s

A 9×1 strip of 0.1″ header pins and a 9×1 strip of 0.1″ right-angle header pins are included, as shown in the picture below. You can solder the header strip of your choice to the board for use with custom cables or solderless breadboards, or you can solder wires directly to the board itself for more compact installations.

Using the L3GD20

Connections

Regardless of the interface being used to communicate with the L3GD20, its VIN pin should be connected to a 2.5-5.5 V source, and GND should be connected to 0 volts. (Alternatively, if you are using the gyro with a 3.3 V system, you can leave VIN disconnected and bypass the built-in regulator by connecting 3.3 V directly to VDD.)

To use the L3GD20 in the default SPI mode, four logic connections are required: SPC, SDI, SDO, and CS. These should be connected to an SPI bus operating at the same logic level as VIN. The SPI interface operates in 4-wire mode by default, with SDI and SDO on separate pins, but it can be configured to use 3-wire mode so that SDO shares a pin with SDI.

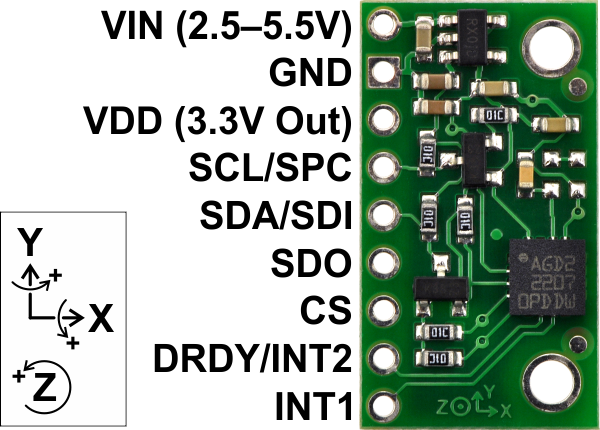

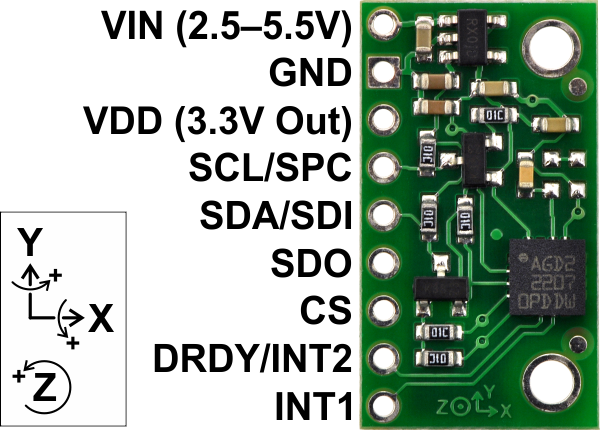

L3GD20 3-axis gyro carrier with voltage regulator, labeled top view.

L3G4200D/L3GD20 3-axis gyro carrier with voltage regulator in a breadboard.

Pinout

PIN Description

VIN This is the main 2.5-5.5 V power supply connection. The SCL/SPC and SDA/SDI level shifters pull the I²C and SPI bus high bits up to this level.

GND The ground (0 V) connection for your power supply. Your I²C or SPI control source must also share a common ground with this board.

VDD Regulated 3.3 V output. Almost 150 mA is available to power external components. (If you want to bypass the internal regulator, you can instead use this pin as a 3.3 V input with VIN disconnected.)

SCL/SPC Level-shifted I²C/SPI clock line: HIGH is VIN, LOW is 0 V

SDA/SDI Level-shifted I²C data line and SPI data in line (also doubles as SDO in 3-wire mode): HIGH is VIN, LOW is 0 V

SDO SPI data out line in 4-wire mode: HIGH is VDD, LOW is 0 V. This output is not level-shifted. Also used as an input to determine I²C slave address (see below).

CS SPI enable (chip select). Pulled up to VDD to enable I²C communication by default; drive low to begin SPI communication.

DRDY/INT2 Data ready indicator, a 3.3-V-logic-level output. HIGH (3.3 V) indicates angular rate data can be read. Can also be configured as a FIFO interrupt. This output is not level-shifted.

INT1 Programmable interrupt, a 3.3-V-logic-level output. This output is not level-shifted.

Schematic Diagram

The above schematic shows the additional components the carrier board incorporates to make the L3GD20 easier to use, including the voltage regulator that allows the board to be powered from a 2.5-5.5 V supply and the level-shifter circuit that allows for I²C and SPI communication at the same logic voltage level as VIN.

I²C Communication

With the CS pin in its default state (pulled up to VDD), the L3GD20 can be configured and its angular velocity readings can be queried through the I²C bus. Level shifters on the I²C clock (SCL) and data (SDA) lines enable I²C communication with microcontrollers operating at the same voltage as VIN (2.5-5.5 V). A detailed explanation of the I²C interface on the L3GD20 can be found in its datasheet (2MB pdf), and more detailed information about I²C in general can be found in NXP’s I²C-bus specification (371k pdf).

In I²C mode, the gyro’s 7-bit slave address has its least significant bit (LSb) determined by the voltage on the SDO pin. The carrier board pulls SDO to VDD through a 10 kΩ resistor, making the LSb 1 and setting the slave address to 1101011b by default. If the gyro’s selected slave address happens to conflict with some other device on your I²C bus, you can drive SDO low to set the LSb to 0.

In our tests of the board, we were able to communicate with the chip at clock frequencies up to 400 kHz; higher frequencies might work but were not tested.

SPI Communication

To communicate with the L3GD20 in SPI mode, the CS pin (which the board pulls to VDD through a 10 kΩ resistor) must be driven low before the start of an SPI command and allowed to return high after the end of the command. Level shifters on the SPI clock (SPC) and data in (SDI) lines enable SPI communication with microcontrollers operating at the same voltage as VIN (2.5-5.5 V).

In the default 4-wire mode, the gyro transmits data to the SPI master on a dedicated data out (SDO) line. If the SPI interface is configured to use 3-wire mode instead, the SDI line doubles as SDO and is driven by the L3GD20 when it transmits data to the master. A detailed explanation of the SPI interface on the L3GD20 can be found in its datasheet (2MB pdf).